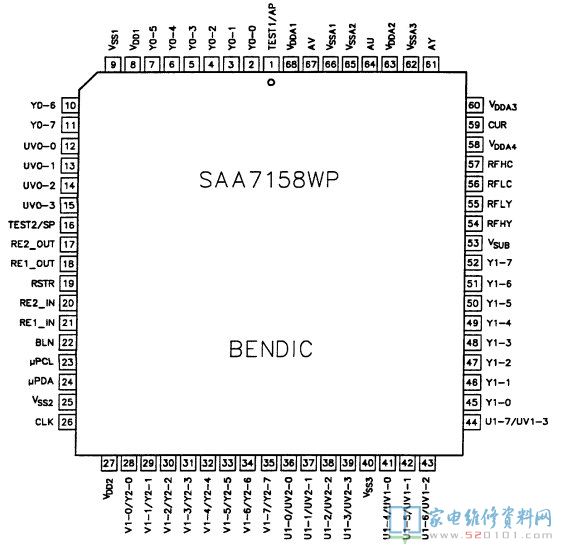

概述:SAA7158是飞利浦半导体(NXP Semiconductors)出品的一款后端集成电路(Back END IC),其主要设计用于与8051型CPU微处理器,系统支持数字Y/U/V总线选择不同的视频信号源。SAA7158采用68引脚PLCC封装工艺。

一、SAA7158功能和特性

* 通过中值滤波降低线路闪烁(LFR)

* 垂直缩放

* 数字色彩瞬态改善

* 数字亮度峰值

* 电影相位检测

*可选4:4:4 YUV数据吞吐量,标准为4:1:1 Y/U/V

* D/A转换

* UART接口。

二、SAA7158引脚功能

| 脚号 | 符号 | 类型 | 功能描述 |

| 1 | TEST1/AP | 输入测试操作管脚:连到Vss | |

| 2 | Y0—0 | 三态输出 | 反馈数据到第二存储器:Y的0位 |

| 3 | Y0—1 | 三态输出 | 反馈数据到第二存储器:Y的1位 |

| 4 | Y0—2 | 三态输出 | 反馈数据到第二存储器:Y的2位 |

| 5 | Y0—3 | 三态输出 | 反馈数据到第二存储器:Y的3位 |

| 6 | Y0—4 | 三态输出 | 反馈数据到第二存储器:Y的4位 |

| 7 | Y0—5 | 三态输出 | 反馈数据到第二存储器:Y的5位 |

| 8 | VDD1 | 供电 | 数字供电电压(+5V) |

| 9 | VSS1 | 地 | 数字地 |

| 10 | Y0—6 | 三态输出 | 反馈数据到第二存储器:Y的6位 |

| 11 | Y0—7 | 三态输出 | 反馈数据到第二存储器:Y的7位 |

| 12 | UV0—0 | 三态输出 | 反馈数据到第二存储器:Y的0位 |

| 13 | UV0—1 | 三态输出 | 反馈数据到第二存储器:Y的1位 |

| 14 | UV0—2 | 三态输出 | 反馈数据到第二存储器:Y的2位 |

| 15 | UV0—3 | 三态输出 | 反馈数据到第二存储器:Y的3位 |

| 16 | TEST2/SP | 输入 | 测试偏移管脚:连到Vss |

| 17 | RE2-OUT | 输入 | 重定可写信号到存储器2 |

| 18 | RE1-OUT | 输入 | 重定可写信号到存储器1 |

| 19 | RSTR | 输入 | 读存储器,uP接口和节目检测复位 |

| 20 | RE2—IN | 输入 | 可写信号到存储器2输入 |

| 21 | RE1—IN | 输入 | 可写信号到存储器1输入 |

| 22 | BLN | 输入 | 消隐信号 |

| 23 | UPCL | 输入 | 8051 UART方式0时钟接口 |

| 24 | UPDA | 输入/输出 | 8051 UART方式0数据接口 |

| 25 | VSS2 | 地 | 数字地 |

| 26 | CLK | 输入 | 主时钟:名义上27(32)MHz |

| 27 | VDD2 | 供电 | 数字供电(+5V) |

| 28 | V1-0/Y2-0 | 输入 | 4:4:4中V的0位:第二存储器Y的0位 |

| 29 | V1-1/Y2-1 | 输入 | 4:4:4中V的1位:第二存储器Y的1位 |

| 30 | VI-2//Y2-2 | 输入 | 4:4:4中V的2位:第二存储器Y的2位 |

| 31 | V1-3/Y2-3 | 输入 | 4:4:4中V的3位:第二存储器Y的3位 |

| 32 | V1-4/Y2-4 | 输入 | 4:4:4中V的4位:第二存储器Y的4位 |

| 33 | V1-5/Y2-5 | 输入 | 4:4:4中V的5位:第二存储器Y的5位 |

| 34 | V1-6/Y2-6 | 输入 | 4:4:4中V的6位:第二存储器Y的6位 |

| 35 | V1-7/Y2-7 | 输入 | 4:4:4中V的6位:第二存储器Y的7位 |

| 36 | U1-0/UV2-0 | 输入 | 4:4:4中U的0位:第二存储器UV的0位 |

| 37 | U1-1/UV2-1 | 输入 | 4:4:4中U的1位:第二存储器UV的1位 |

| 38 | U1-2/UV2-2 | 输入 | 4:4:4中U的2位:第二存储器UV的2位 |

| 39 | U1-3/UV2-3 | 输入 | 4:4:4中U的3位:第二存储器UV的3位 |

| 40 | VSS3 | 地 | 数字地 |

| 41 | U1-4/UV1-0 | 输入 | 4:4:4中U的4位:第二存储器UV的0位 |

| 42 | U1-5/UV1-1 | 输入 | 4:4:4中U的5位:第二存储器UV的1位 |

| 43 | U1-6/UV1-2 | 输入 | 4:4:4中U的6位:第二存储器UV的2位 |

| 44 | U1-7/UV1-3 | 输入 | 4:4:4中U的7位:第二存储器UV的3位 |

| 45 | Y1—0 | 输入 | 第一存储器Y的0位 |

| 46 | Y1—1 | 输入 | 第一存储器Y的1位 |

| 47 | Y1—2 | 输入 | 第一存储器Y的2位 |

| 48 | Y1—3 | 输入 | 第一存储器Y的3位 |

| 49 | Y1—4 | 输入 | 第一存储器Y的4位 |

| 50 | Y1—5 | 输入 | 第一存储器Y的5位 |

| 51 | Y1—6 | 输入 | 第一存储器Y的6位 |

| 52 | Y1—7 | 输入 | 第一存储器Y的7位 |

| 53 | VSS | 模拟地 | 基准管脚:连到模拟地(VSSA) |

| 54 | RFHY | 模拟输入 | 连C=100nF到模拟地(VSSA) |

| 55 | RFLY | 模拟输入 | 连到模拟地(VSSA) |

| 56 | RFLC | 模拟输入 | 连到模拟地(VSSA) |

| 57 | RFHC | 模拟输入 | 连到模拟地(VSSA) |

| 58 | VDDA4 | 模拟供电 | 三个参考模数转换阶梯信号发生器及输出缓冲的电流源的模拟电压 |

| 59 | CUR | 模拟输入 | 模拟输出缓冲电流输入(0.4mA从VDDA4=5V:接R=15K) |

| 60 | VDDA3 | 模拟供电 | 输出缓冲AY模拟供电 |

| 61 | AY | 模拟输出 | 模拟亮度Y输出 |

| 62 | VSSA3 | 模拟地 | 输出缓冲AY模拟地 |

| 63 | VDDA2 | 模拟供电 | 输出缓冲AN模拟供电 |

| 64 | AU | 模拟输出 | 模拟(B-Y)或-(B-Y)输出 |

| 65 | VSSA2 | 模拟地 | 输出缓冲AU模拟地 |

| 66 | VSSA1 | 模拟地 | 输出缓冲AV模拟地 |

| 67 | AV | 模拟输出 | 模拟(R-Y)或-(R-Y)输出 |

| 68 | VDDA1 | 供电 | 输出缓冲AV模拟供电 |

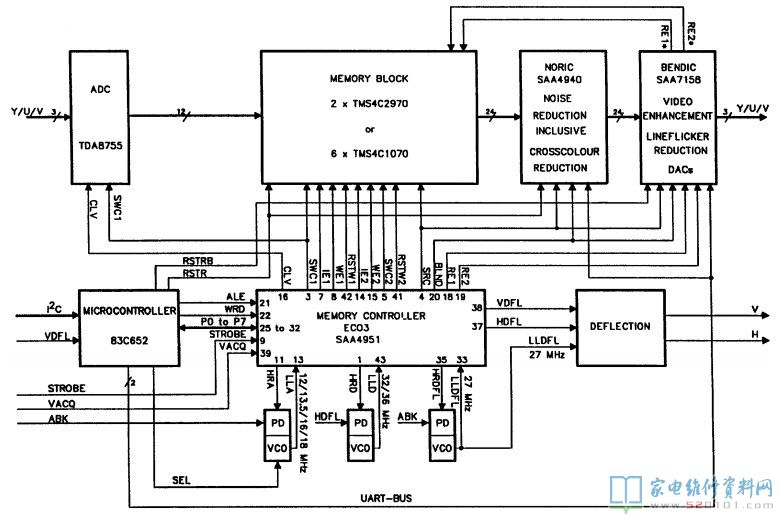

二、SAA7158内部方框图

网友评论