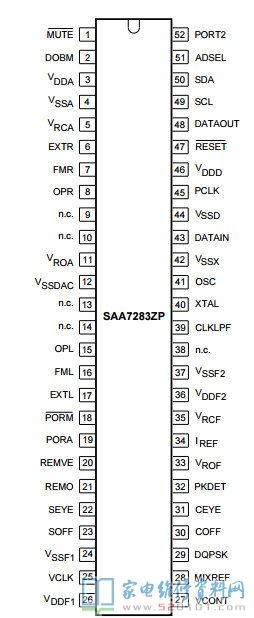

概述:SAA7283ZP是飞利浦半导体(NXP Semiconductors)出品的一款第三代数字声解码器(第一代为SAA7280、第二代为SAA7282),它是高集成度CMOS电路,由丽音解调电路、丽音解码电路、数模变换电路、调频信号/丽音信号电平匹配与切换电路等组成。SAA7283ZP采用高信能的CMOS模拟信号处理电路,因此在弱信号情况下,也可以保证高质量的声音再现。SAA7283ZP采用先进的比特流变换技术,它还具有数字声输出接口电路,数字声接口电路等。SAA7283ZP采用52引脚SDIP封装工艺。

一、SAA7283ZP引脚功能与实测电压

| 脚号 | 符号 | 功能说明 | 有信号电压/V | 红笔接地/KΩ | 黑笔接地/KΩ |

| 1 | MUTE | 静音控制(低电平有效) | 4.3 | 9.9 | 6 |

| 2 | DOBM | 数字音频信号输出 | 2.1 | 9.9 | 6 |

| 3 | VDDA | 音频通道模拟电路5V供电 | 4.3 | 6.4 | 4.4 |

| 4 | VSSA | 音频通道模拟电路地 | 0 | 7.4 | 6 |

| 5 | VRCA | 内部音频参考电压 | 2.2 | 7.4 | 6 |

| 6 | EXTR | 外音频右声道输入(模拟) | 0.2 | 7.4 | 5.9 |

| 7 | FMR | R声道调频伴音输入 | 0.3 | 7.4 | 5.9 |

| 8 | OPR | R声道音频输出(模拟) | 2.2 | 7.4 | 5.9 |

| 9-10 | NC | 空 | 0 | ∞ | ∞ |

| 11 | VROA | 内音频参考电压缓冲输出 | 2.2 | 8 | 5.3 |

| 12 | VSSDAC | D/A变换地 | 0 | 0 | 0 |

| 13-14 | NC | 空 | 0 | ∞ | ∞ |

| 15 | OPL | 左声道模拟音频输出 | 2.2 | 7.4 | 5.9 |

| 16 | FML | L声道调频伴音输入 | 0.3 | 7.4 | 5.9 |

| 17 | EXTL | 外部L声道输入 | 0.3 | 7.4 | 5.9 |

| 18 | PORM | 开机静音控制输入 | 4 | 8.2 | 5.9 |

| 19 | PORA | 开机后音频选择控制输入 | 0 | 0 | 0 |

| 20 | REMVE | 载波环路滤波 | 2.1 | 7.5 | 5.7 |

| 21 | REMO | 载波环路滤波输出 | 2.3 | 7.5 | 5.7 |

| 22 | SEYE | 正弦通道监视输出 | 2.1 | 7.4 | 5.9 |

| 23 | SOFF | 正弦通道偏置补偿电容 | 2 | 0 | 0 |

| 24 | VssF1 | 解调地 | 0 | 0 | 0 |

| 25 | VCLK | 监视用PLL环路VCO时钟输出 | 2.2 | 10.2 | 6 |

| 26 | VDDFI | 解调电路供电 | 4.5 | ∞ | ∞ |

| 27 | VCONT | PLL环路控制电压输入 | 2.1 | 10.2 | 6 |

| 28 | MIXREF | 混频参考电压 | 2.1 | 7.5 | 6 |

| 29 | DQPSK | DQPSK信号输入 | 2.1 | 7.5 | 5.9 |

| 30 | COFF | 余弦通道偏置补偿电容 | 1.9 | 8 | 5.6 |

| 31 | CEYE | 余弦通道监视图输出 | 2.1 | 11.2 | 6 |

| 32 | PKDET | 外接封值AGC检波电容 | 0.1 | 7.4 | 6 |

| 33 | VROF | 内部解调参考电压缓冲输出 | 2.1 | 7.6 | 5.3 |

| 34 | IREF | 内部解调参考电流输出 | 2 | 6.9 | 5.7 |

| 35 | VRCF | 内部解调参考电压非缓冲输出 | 2.1 | 7.1 | 6 |

| 36 | VDDF2 | 解调电路供电电压输出 | 4.1 | 6.3 | 4.4 |

| 37 | VssF2 | 解调电路地 | 0 | 0 | 0 |

| 38 | NC | 空 | 4.3 | 6 | 6 |

| 39 | CLKPF | 时钟PLL比较器输出 | 0 | 6 | 6 |

| 40 | XTAL | 外接8.192MHz晶体输入 | 3 | 6 | 6 |

| 41 | OSC | 外接8.192MHz晶体输出 | 2 | 5.7 | 5.7 |

| 42 | VSSN | 晶振地 | 0 | 0 | 0 |

| 43 | DATAIN | 728bits串行数据输入 | 2 | 5.8 | 5.8 |

| 44 | VSSD | 数字电路地 | 2.2 | 0 | 0 |

| 45 | PCLK | 728K时钟输出至DQPSK解调器 | 2.2 | 6.7 | 6.7 |

| 46 | VDDD | 数字电源 | 4.3 | 4.4 | 4.4 |

| 47 | RESET | 复位(低电平)输入 | 4.5 | 6 | 6 |

| 48 | DATAOUT | DQPSK解调器728bits串行输出 | 2 | 5.8 | 5.8 |

| 49 | SCL | I2C总线时钟线 | 3.9 | 6 | 6 |

| 50 | SDA | I2C总线数据线 | 3.2 | 6 | 6 |

| 51-52 | - | 空 | - | - | - |

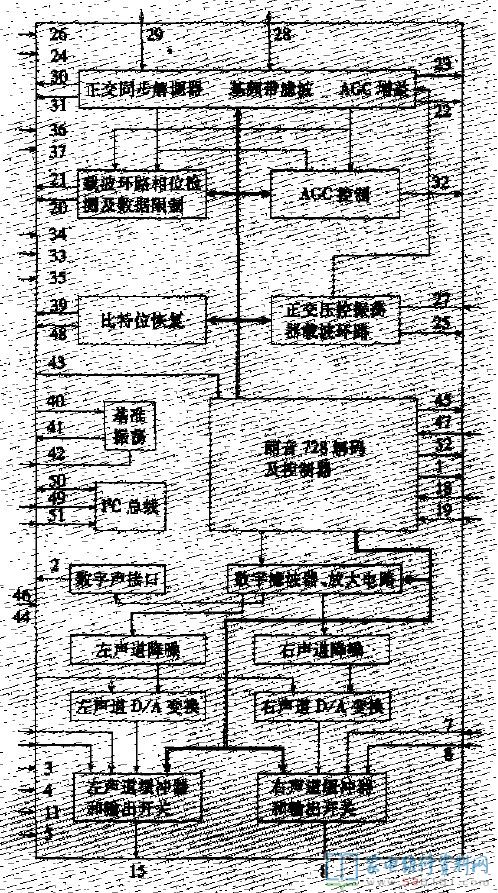

二、SAA7283ZP内部方框图

上面的电路方框图中,其具备DQPSK滤波器内藏, 内置正交分频器,AGC放大器,自动静音功能电路,多制式的NICAM解码器,可接收PAL,D/K,I,B/G及法国丽音等,I C总线控制。

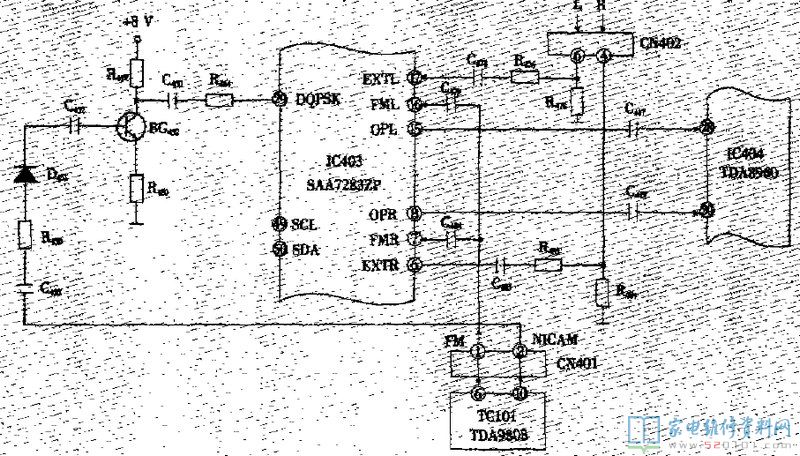

三、SAA7283ZP典型应用电路

网友评论