概述:FLI2300是Genesis公司生产的高质量数字视频格式变换器,它用于CRT-TV的高整合数字视频转换的专利应用软件,具有非线性和任意图形缩放比例、帧频比例转换,它的内部集成的三个10位模数变换器,还具有高质量视频处理技术Faroudja(TM),发挥专利和艾米奖视频处理技术的优势。

一、FLI2300引脚功能说明

| 引脚 |

引脚名称 |

I/O类型 |

功能描述 |

| 1 |

HSYNC1-PORT1 |

INPUT输入 |

水平同步或参考-CTL1 |

| 2 |

VSYNC1-PORT1 |

INPUT输入 |

垂直同步或参考-CTL1 |

| 3 |

FIELDID1--PORT1 |

INPUT输入 |

奇数/偶数扫描场识别-CTL1 |

| 4 |

IN-CLK-PORT1 |

INPUT输入 |

时钟、数据输入-CTL1 |

| 5 |

HSYNC2-PORT1 |

INPUT输入 |

水平同步或参考-CTL2 |

| 6 |

VSYNC2-PORT1 |

INPUT输入 |

垂直同步或参考-CTL2 |

| 7 |

FIELDID2—PORT2 |

INPUT输入 |

奇数/偶数扫描场识别-CTL2 |

| 8/30/48 62/88 112/128 146/193 |

VDD |

POWER电源 |

3.3V |

| 9/31/49 63/89 113/129 147/194 |

VSS |

GROUND |

接地 |

| 10 |

IN-CLK-PORT1 |

INPUT输入 |

时钟、数据输入-CTL2 |

| 11 |

B/CB/D1-0 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 12 |

B/CB/D1-1 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 13 |

B/CB/D1-2 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 14 |

B/CB/D1-3 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 15 |

B/CB/D1-4 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 16/36 68/80 96/123 138/197 |

VDDcore |

Power电源 |

1.8V-电源输入核心脚 |

| 17/37 69/81 97/124 139/198 |

VSScore |

GROUND地 |

接脚 |

| 18 |

B/CB/D1-5 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 19 |

B/CB/D1-6 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 20 |

B/CB/D1-7 |

INPUT输入 |

接口1-数字视频输入(B /CB/D1) |

| 21 |

R/CR/CB CR-0 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 22 |

R/CR/CB CR-1 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 23 |

R/CR/CB CR-2 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 24 |

R/CR/CB CR-3 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 25 |

R/CR/CB CR-4 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 26 |

R/CR/CB CR-5 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 27 |

R/CR/CB CR-6 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 28 |

R/CR/CB CR-7 |

INPUT输入 |

接口1-数字视频输入(R /CB/D1) |

| 29 |

G/Y/Y-0 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 32 |

G/Y/Y-1 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 33 |

G/Y/Y-2 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 34 |

G/Y/Y-3 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 35 |

G/Y/Y-4 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 38 |

G/Y/Y-5 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 39 |

G/Y/Y-6 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 40 |

G/Y/Y-7 |

INPUT输入 |

接口1-数字视频输入(G /Y) |

| 41 |

IN-SEL |

OUTPUT输出 |

输出到外部视频选择(NC空脚) |

| 42/90 |

TEST |

INPUT输入 |

测试接通到地 |

| 43 |

DEV-ADDR1 |

INPUT输入 |

设计地址调整1 |

| 44 |

DEV-ADDR0 |

INPUT输入 |

设计地址调整0 |

| 45 |

SCLK |

I/O |

IIC总线控制:时钟线 |

| 46 |

SDATA |

I/O |

IIC总线控制:数据线 |

| 47 |

RESET-N |

INPUT输入 |

复位 |

| 50 |

SDRAM DATA(0) |

TRISTATE I/O |

SDRAM数据总线 |

| 51 |

SDRAM DATA(1) |

TRISTATE I/O |

SDRAM数据总线 |

| 52 |

SDRAM DATA(2) |

TRISTATE I/O |

SDRAM数据总线 |

| 53 |

SDRAM DATA(3) |

TRISTATE I/O |

SDRAM数据总线 |

| 54 |

SDRAM DATA(4) |

TRISTATE I/O |

SDRAM数据总线 |

| 55 |

SDRAM DATA(5) |

TRISTATE I/O |

SDRAM数据总线 |

| 56 |

SDRAM DATA(6) |

TRISTATE I/O |

SDRAM数据总线 |

| 57 |

SDRAM DATA(7) |

TRISTATE I/O |

SDRAM数据总线 |

| 58 |

SDRAM DATA(8) |

TRISTATE I/O |

SDRAM数据总线 |

| 59 |

SDRAM DATA(9) |

TRISTATE I/O |

SDRAM数据总线 |

| 60 |

SDRAM DATA(10) |

TRISTATE I/O |

SDRAM数据总线 |

| 61 |

SDRAM DATA(11) |

TRISTATE I/O |

SDRAM数据总线 |

| 64 |

SDRAM DATA(12) |

TRISTATE I/O |

SDRAM数据总线 |

| 65 |

SDRAM DATA(13) |

TRISTATE I/O |

SDRAM数据总线 |

| 66 |

SDRAM DATA(14) |

TRISTATE I/O |

SDRAM数据总线 |

| 67 |

SDRAM DATA(15) |

TRISTATE I/O |

SDRAM数据总线 |

| 70 |

SDRAM DATA(16) |

TRISTATE I/O |

SDRAM数据总线 |

| 71 |

SDRAM DATA(17) |

TRISTATE I/O |

SDRAM数据总线 |

| 72 |

SDRAM DATA(18) |

TRISTATE I/O |

SDRAM数据总线 |

| 73 |

SDRAM DATA(19) |

TRISTATE I/O |

SDRAM数据总线 |

| 74 |

SDRAM DATA(20) |

TRISTATE I/O |

SDRAM数据总线 |

| 75 |

SDRAM DATA(21) |

TRISTATE I/O |

SDRAM数据总线 |

| 76 |

SDRAM DATA(22) |

TRISTATE I/O |

SDRAM数据总线 |

| 77 |

SDRAM DATA(23) |

TRISTATE I/O |

SDRAM数据总线 |

| 78 |

SDRAM DATA(24) |

TRISTATE I/O |

SDRAM数据总线 |

| 79 |

SDRAM DATA(25) |

TRISTATE I/O |

SDRAM数据总线 |

| 82 |

SDRAM DATA(26) |

TRISTATE I/O |

SDRAM数据总线 |

| 83 |

SDRAM DATA(27) |

TRISTATE I/O |

SDRAM数据总线 |

| 84 |

SDRAM DATA(28) |

TRISTATE I/O |

SDRAM数据总线 |

| 85 |

SDRAM DATA(29) |

TRISTATE I/O |

SDRAM数据总线 |

| 86 |

SDRAM DATA(30) |

TRISTATE I/O |

SDRAM数据总线 |

| 87 |

SDRAM DATA(31) |

TRISTATE I/O |

SDRAM数据总线 |

| 91 |

SDRAM ADDR(10) |

TRISTATE O/P |

SDRAM地址总线 |

| 92 |

SDRAM ADDR(9) |

TRISTATE O/P |

SDRAM地址总线 |

| 93 |

SDRAM ADDR(8) |

TRISTATE O/P |

SDRAM地址总线 |

| 94 |

SDRAM ADDR(7) |

TRISTATE O/P |

SDRAM地址总线 |

| 95 |

SDRAM ADDR(6) |

TRISTATE O/P |

SDRAM地址总线 |

| 98 |

SDRAM ADDR(5) |

TRISTATE O/P |

SDRAM地址总线 |

| 99 |

SDRAM ADDR(4) |

TRISTATE O/P |

SDRAM地址总线 |

| 100 |

SDRAM ADDR(3) |

TRISTATE O/P |

SDRAM地址总线 |

| 101 |

SDRAM ADDR(2) |

TRISTATE O/P |

SDRAM地址总线 |

| 102 |

SDRAM ADDR(1) |

TRISTATE O/P |

SDRAM地址总线 |

| 103 |

SDRAM ADDR(0) |

TRISTATE O/P |

SDRAM地址总线 |

| 104 |

SDRAM WEN |

TRISTATE O/P |

SDRAM可写入脚 |

| 105 |

SDRAM RASN |

TRISTATE O/P |

SDRAM选择地址行 |

| 106 |

SDRAM CASN |

TRISTATE O/P |

SDRAM选择地址排 |

| 107 |

SDRAM BA1 |

TRISTATE O/P |

SDRAM选择口1 |

| 108 |

SDRAM BA0 |

TRISTATE O/P |

SDRAM选择口0 |

| 109 |

SDRAM CSN |

TRISTATE O/P |

SDRAM CS* |

| 110 |

SDRAM DQM |

TRISTATE O/P |

SDRAM DQM* |

| 111 |

SDRAM CLKOUT |

OUTPUT输出 |

时钟输出到SDRAM * |

| 114 |

SDRAM CLKIN |

INPUT输入 |

SDRAM时钟延时跟踪输入 |

| 115 |

TEST3 |

INPUT输入 |

测试输入到地连接 |

| 116 |

TEST OUT0 |

OUTPUT输出 |

测试输出0 |

| 117 |

TEST OUT1 |

OUTPUT输出 |

测试输出1 |

| 118 |

CTL OUT0 |

TRISTATE O/P |

行同步输出 |

| 119 |

CTL OUT1 |

TRISTATE O/P |

场同步输出 |

| 120 |

CTL OUT2 |

TRISTATE O/P |

NC空脚 |

| 121 |

CTL OUT3 |

TRISTATE O/P |

NC空脚 |

| 122 |

CTL OUT4 |

TRISTATE O/P |

NC空脚 |

| 125 |

CLK OUT |

RISTATE O/P |

输出数据比率时钟NC |

| 136 |

B/U/PB-OUT-0 |

RISTATE O/P |

NC空脚 |

| 127 |

B/U/PB-OUT-1 |

RISTATE O/P |

NC空脚 |

| 130 |

B/U/PB-OUT-2 |

RISTATE O/P |

NC空脚 |

| 131 |

B/U/PB-OUT-3 |

RISTATE O/P |

NC空脚 |

| 132 |

B/U/PB-OUT-4 |

RISTATE O/P |

NC空脚 |

| 133 |

B/U/PB-OUT-5 |

RISTATE O/P |

NC空脚 |

| 134 |

B/U/PB-OUT-6 |

RISTATE O/P |

NC空脚 |

| 135 |

B/U/PB-OUT-6 |

RISTATE O/P |

NC空脚 |

| 136 |

R/V/PR-OUT0 |

RISTATE O/P |

NC空脚 |

| 137 |

R/V/PR-OUT1 |

RISTATE O/P |

NC空脚 |

| 140 |

R/V/PR-OUT2 |

RISTATE O/P |

NC空脚 |

| 141 |

R/V/PR-OUT3 |

RISTATE O/P |

NC空脚 |

| 142 |

R/V/PR-OUT4 |

RISTATE O/P |

NC空脚 |

| 143 |

R/V/PR-OUT5 |

RISTATE O/P |

NC空脚 |

| 144 |

R/V/PR-0UT6 |

RISTATE O/P |

NC空脚 |

| 145 |

R/V/PR-0UT7 |

RISTATE O/P |

NC空脚 |

| 148 |

G/Y/Y-OUT0 |

RISTATE O/P |

NC空脚 |

| 149 |

G/Y/Y-OUT1 |

RISTATE O/P |

NC空脚 |

| 150 |

G/Y/Y-OUT2 |

RISTATE O/P |

NC空脚 |

| 151 |

G/Y/Y-OUT3 |

RISTATE O/P |

NC空脚 |

| 152 |

G/Y/Y-OUT4 |

RISTATE O/P |

NC空脚 |

| 153 |

G/Y/Y-OUT5 |

RISTATE O/P |

NC空脚 |

| 154 |

G/Y/Y-OUT6 |

RISTATE O/P |

NC空脚 |

| 155 |

G/Y/Y-OUT7 |

RISTATE O/P |

NC空脚 |

| 156 |

OE |

INPUT输入 |

接+3.3V供电 |

| 157 |

PLL-PVDD |

POWER电源 |

1.8V |

| 158 |

PLL-VSS |

GROUND地 |

接地 |

| 159 |

AVSS-PLL-BE1 |

GROUND地 |

接地 |

| 160 |

AVDD-PLL-BE1 |

POWER电源 |

1.8V |

| 161 |

AVDD-PLL-BE2 |

POWER电源 |

1.8V |

| 162 |

AVSS-PLL-BE2 |

GROUND地 |

接地 |

| 163 |

AVSS-PLL-SD1 |

GROUND地 |

接地 |

| 164 |

AVDD-PLL-SD1 |

POWER电源 |

1.8V |

| 165 |

AVDD-PLL-FE |

POWER电源 |

1.8V |

| 166 |

AVSS-PLL-FE |

GROUND地 |

接地 |

| 167/169/172 175/178/184 185 |

DAC-VSS |

GROUND地 |

接地 |

| 168 |

DAC-VDD |

POWER电源 |

1.8V |

| 170 |

DAC-BOUT |

OUTPUT输出 |

B蓝色输出 |

| 171 |

DAC-AVDDB |

POWER电源 |

3.3V |

| 173 |

DAC-GOUT |

OUTPUT输出 |

G绿色输出 |

| 174 |

DAC-AVDDG |

POWER电源 |

3.3V |

| 176 |

DAC-ROUT |

OUTPUT输出 |

R红色输出 |

| 177 |

DAC-AVDDR |

POWER电源 |

3.3V |

| 179 |

DAC-COMP |

OUTPUT输出 |

视频补偿DACS |

| 180 |

DAC-RSET |

OUTPUT输出 |

DACS复位 |

| 181 |

DAC-VREFOUT |

OUTPUT输出 |

1.28V参考供电DACS |

| 182 |

DAC-VREFIF |

INPUT输入 |

DACS视频外部电压参考输入 |

| 183 |

DAC-AVDD |

POWER电源 |

3.3V |

| 186/187 |

DAC-GR-AVDD |

POWER电源 |

3.3V |

| 188/189/190 |

TEST |

INPUT输入 |

接地 |

| 191 |

XTAL IN |

INPUT输入 |

晶体振荡输入 |

| 192 |

XTAL OUT |

OUTPUT输出 |

晶体振荡输出 |

| 195 |

IN-CLK-PORT2 |

INPUT输入 |

接口2:数据时钟输入 |

| 196/199/200 201202/203 204205 |

D1-IN |

INPUT输入 |

BT656数字数据输入 |

| 206 |

FIELDID-PORT2 |

INPUT输入 |

|

| 207 |

VSYNC-PORT2 |

INPUT输入 |

接口2:场同步或参考 |

| 208 |

HSYNC-PORT2 |

INPUT输入 |

接口2:行同步或参考 |

[Page]

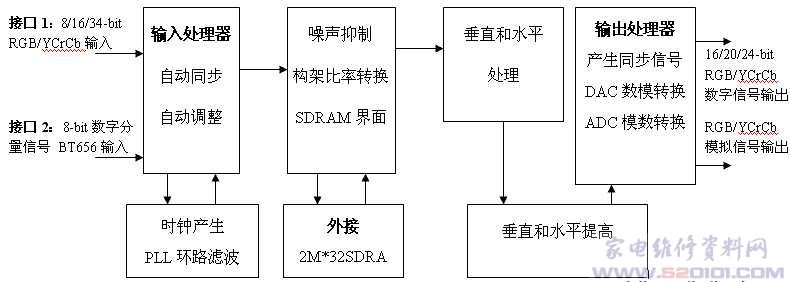

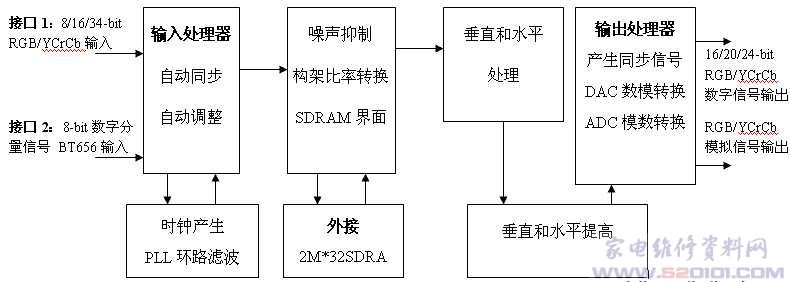

二、FLI2300内部方框图

三、功能和特点

支持100Hz隔行(欧洲方案)

对角线图像处理技术Faroudja DCDi™

串色抑制CCS

电影胶片模式图像质量

运动自适应逐行处理(基于每象素的处理技术)

电影/电视模式识别和处理

还原真实生活的数字视频加强处理TrueLife™

三维运动自适应噪音降低处理

非线性和任意图形缩放比例

帧频比例转换

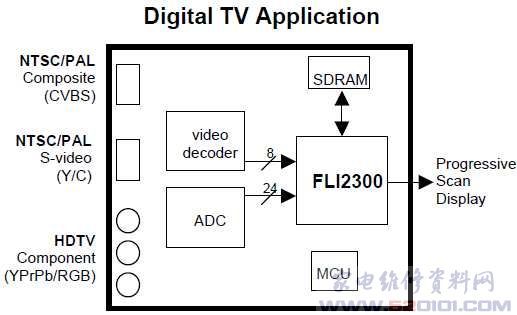

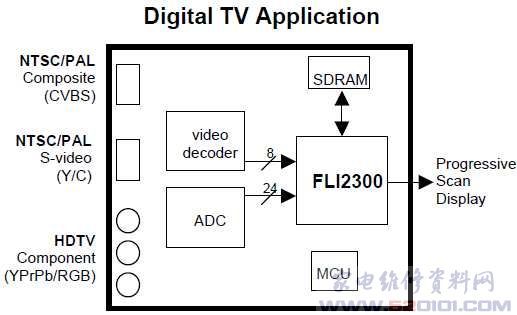

四、典型应用方框图

网友评论